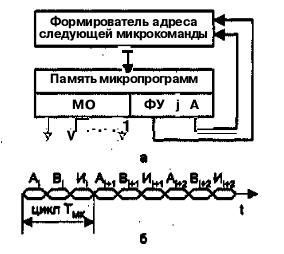

Цикл выполнения микрокоманды Тмк можно представить в виде трех этапов:

• формирования адреса очередной микрокоманды в ФАМ (Ai);

• выборки по данному адресу микрокоманды из памяти микропрограмм (B);

• исполнения микрокоманды в операционной (ОЧ) или адресной части (АЧ) вычислительной машины (И).

Порядок следования этапов определяется способом соединения формирователя адреса следующей микрокоманды и памяти микропрограмм.

Структура МПА с ФАМ и ПМП, связанными непосредственно друг с другом, не допускает совмещения этапов во времени - здесь этап Аi+1 начинается только после выполнения этапа И i.

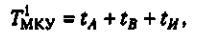

В течение цикла Тмк все узлы заняты обработкой только одной, текущей микрокоманды с номером i, причем последовательный характер обработки МК не позволяет достичь высокого быстродействия:

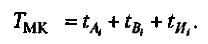

Производительность ВМ повышается при одновременной конвейерной обработке в МПА нескольких микрокоманд, находящихся на различных этапах выполнения. Для совмещения во времени этапов Ai, Вi и Иi МПА вводятся дополнительный элементы, которые хранят результаты обработки на каждом этапе.

В МПА с одним уровнем совмещения Используется один запоминающий элемент - конвейерный регистр микрокоманды, подключенный к выходу памяти микропрограмм. В данной структуре реализуется одновременная обработка двух микрокоманд: в то время как исполняется находящаяся в РМК i-я микрокоманда (этап Иi,), в ФАМ вычисляется адрес (i + 1)-й микрокоманды (этап Ai+1), и затем по этому адресу из ПМП выбирается (i + 1)-я микрокоманда (этап Вi+1). Следовательно, в МПА с одним уровнем совмещения обеспечивается параллельное выполнение этапов Ai+1 и Вi+1 и этапа Иi.

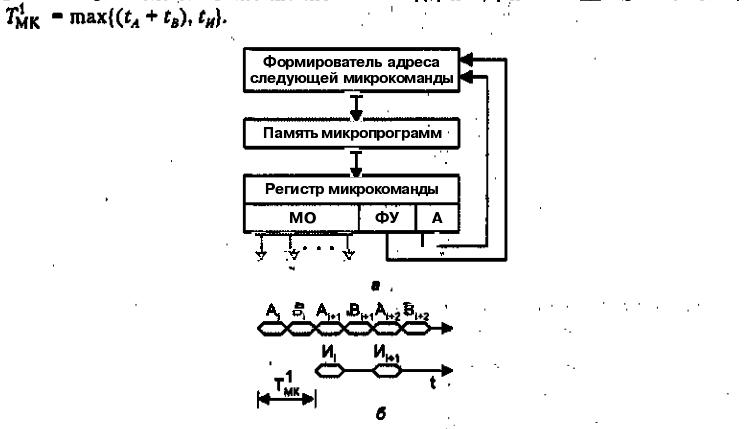

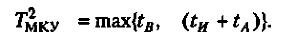

Очевидно, что при tи < ta + tb данной структуре наблюдается вынужденный простой операционной (или адресной) части ВМ. Этот недостаток устраняется в МПА с двумя уровнями совмещения, в котором ФАМ и ПМП связаны друг с другом двумя конвейерными регистрами - РМК и РАМ. Здесь одновременно обрабатываются три микрокоманды: в операционной или адресной части исполняется МКi (этап Иi) выбирается из памяти МКi+1(этап Bi+1),а в ФАМ вычисляется адрес М(этап Ai+2). В такой структуре совмещается во времени выполнение всех трех этапов Тмк= тах{(ta, tb, tu)}.

Методы конвейерной обработки обеспечивают значительный выигрыш только при выполнении линейных участков микропрограммы. Если реализуемая в ФАМ функция управления является условной, а значение условия вырабатывается на текущем этапе в операционной (адресной) части, то правильный адрес следующей микрокоманды может быть вычислен только по окончании этапа И, ответственного за выработку значения условия перехода. В итоге длительность цикла для МПА

с одним уровнем совмещения увеличивается до величины

а для МПА с двумя уровнями совмещения - до величины

а для МПА с двумя уровнями совмещения - до величины

Всего, в зависимости от использования регистров - регистра РМК, состоящего из адресной и микрооперационной частей, регистра РАМ, регистра состояния РГС (для хранения условия перехода), - можно сформировать 11 различных структур МПА Эти структуры. Выбор оптимальной структуры определяется особенностями конкретной микропрограммы.

Вернутся к заглавию